Motivazioni della ricerca

I dispositivi PLL sono stati ideati nel 1932 e si sono sempre piu' affermati nel campo dell’elettronica, sia analogica che digitale, in numerosi campi di applicazione. Tra i tanti, citiamo:

-

-recupero del clock e dei dati (clock/data recovery)

-

-phase shifter;

-

-moltiplicazione di frequenza;

-

-sincronizzazione di frequenza;

-

-modulazione e demodulazione (FM o di frequenza, PM o di fase) e in generale sistemi di tuning digitale;

-

-carrier recovery (o recupero della portante);

- controllo di motori.

Molteplici architetture di PLL sono state proposte in letteratura, quasi tutte basate su almeno un dispositivo puramente analogico o sulla possibilita' di agire su un parametro analogico di un dispositivo digitale (ad es. agendo sulla tensione di alimentazione).

Successivamente, nuove architetture all-digital, ossia interamente digitali, hanno fatto il loro ingresso nel ventaglio di soluzioni disponibili per la progettazione di PLL. Tali architetture non hanno dipendenza da alcun elemento analogico o da componenti passivi quali resistori e condensatori, facilmente soggetti a fallimento, nel caso di interazione con radiazioni ionizzanti o esposti a problematiche conseguenti la presenza di elementi parassiti.

I motivi di tale migrazione sono essenzialmente legati alla evoluzione tecnologica della produzione di circuiti integrati. Infatti, inizialmente, i dispositivi PLL basati su elementi analogici sono stati preferiti per applicazioni ad alta frequenza ed elevate prestazioni (ossia a basso phase noise). Tuttavia, l'introduzione delle nuove tecnologie e i continui progressi compiuti nel campo della produzione di circuiti integrati (diminuzione dei costi, aumento delle frequenze di funzionamento, maggiori funzionalita' a parita' di area di silicio) hanno consentito e favorito la realizzazione di PLL completamente digitali e completamente integrabili.

Oltre ai costi ridotti e alla minor area utilizzata, che rendono i PLL completamente digitali degli ottimi candidati per soddisfare piu' a lungo la Legge di Moore, in genere il flusso di progettazione digitale e' di gran lunga piu' semplice del corrispettivo analogico.

Inoltre, un all-digital PLL possiede una minore sensibilita' alle fonti di disturbo, quali le variazioni della tensione di alimentazione e le variazioni parametriche dei componenti con temperatura e invecchiamento (i cosiddetti parametri PVT: Process, Voltage e Temperature). I circuiti analogici sono piu' sensibili ad elementi parassiti rispetto ai circuiti digitali, che, utilizzando segnali discriminati in ampiezza, offrono anche una maggiore immunita' al rumore.

In definitiva, l'approccio all-digital non puo' far altro che migliorare le caratteristiche spettrali dei segnali ricostruiti e l'affidabilita' del circuito.

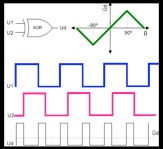

Un PLL (Phase-Locked Loop) e' un particolare circuito a retroazione, che rende possibile la sincronizzazione, in frequenza e in fase, di un segnale di output (generalmente prodotto da un oscillatore) con un segnale di ingresso di riferimento (reference). Quando questo accade, si dice che il sistema e' agganciato (locked) e la differenza di fase (phase error) tra il segnale di uscita e il riferimento e' zero oppure costante.

Nel caso in cui la differenza di fase tra i due segnali cambi, un sistema di controllo agisce sull'oscillatore in modo da ridurre la differenza al minimo.

Un PLL puo' anche essere utilizzato per produrre in uscita un segnale avente una frequenza multipla di quella del segnale di riferimento: in questo caso si parla di frequency synthesis.

Obiettivi del progetto sono lo studio, l'analisi di fattibilita' e l'implementazione di un dispositivo PLL (Phase Locked Loop) e di un CDR (Clock Data Recovery) all-digital, realizzati tramite sviluppo e prototipizzazione su FPGA e successiva implementazione su ASIC.

Lo sviluppo e l'implementazione di un PLL all-digital e di un CDR avrebbero come naturale conseguenza la possibilita' di poter realizzare dispositivi robusti (per costruzione) rispetto ad eventi di Single Event Upset (SEU) e quindi piu' affidabili per l'utilizzo in applicazioni in ambienti esposti a radiazioni ionizzanti. La scelta di un opportuno processo tecnologico per la fabbricazione dei dispositivi garantira' inoltre una buona resistenza ad effetti da dose totale (TID). Inoltre, i PLL all-digital favorirebbero il disegno di link al Gb/s basato su FPGA economiche e potenzialmente radiation-tolerant.