# **CAPITOLO 3**

# La struttura di acquisizione

In questo capitolo si discute l'architettura del sistema di acquisizione dati (DAQ) e del trigger di primo livello dello spettrometro per muoni dell'apparato ATLAS [3]. Viene, dunque, focalizzata l'attenzione sulla sincronizzazione dell'apparato con la macchina acceleratrice LHC, sul sistema di distribuzione dei segnali di controllo e sulla struttura di acquisizione e trasmissione dei dati dai rivelatori RPC alla sala di conteggio USA15.

I segnali degli RPC subiscono diversi stadi di elaborazione prima di essere inviati su fibra ottica alla sala di conteggio *USA15* ed essere trattati dai successivi livelli di acquisizione ed elaborazione. Vengono dunque descritti gli algoritmi delle matrici di coincidenza per la generazione del trigger e la struttura delle altre schede di acquisizione. Successivamente viene passato in rassegna il sistema di trasmissione su fibra ottica, i cui ricevitori sono destinati ad essere alloggiati sul concentratore ottico, sviluppato nel presente lavoro di tesi.

### La sincronizzazione

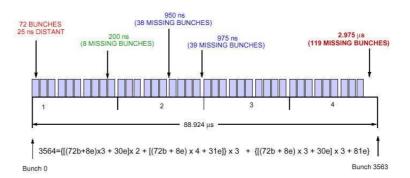

Nei fasci dell'acceleratore LHC i protoni sono raggruppati in pacchetti ("bunches") che si incrociano ed interagiscono (bunch crossing) ogni 25 ns in quattro siti sperimentali, uno dei quali ospita l'esperimento ATLAS. Dal punto di vista del sistema di acquisizione dei dati, l'apparato ATLAS costituisce un sistema sincrono che funziona alla frequenza di interazione dell'LHC, ossia 40 MHz. Per rendere l'apparato ATLAS sincrono con la macchina LHC tutti i sistemi del DAQ e di trigger dovranno essere pilotati da un segnale comune di clock, sincronizzato alla frequenza di bunch crossing dell'acceleratore. Al moto di rivoluzione dei bunches all'interno dell'LHC è associato un segnale periodico, detto orbita. Questo segnale, generato dal sistema di controllo dell'acceleratore LHC, ha un periodo di 88924 ns ed è composto da 3564 elementi, detti anch'essi impropriamente "bunches" in quanto alcuni non contengono protoni. I bunches sono raggruppati in treni, a gruppi di 72. La figura 3.1 mostra la struttura di un intero periodo. In particolare si nota la presenza di lacune (missing bunches) all'interno dell'orbita stessa.

Figura 3.1 Distribuzione dei bunches nell'orbita di LHC

Per una corretta identificazione di un evento interessante per la fisica studiata ad ATLAS è necessario che gli elementi dell'elettronica di acquisizione (elettronica di *front end*) associno in modo univoco ai dati in ogni evento un numero progressivo (*Event Identifier*, o *EVID*) ed uno

identificativo del *bunch crossing* in cui si è generata la collisione ( *Bunch Crossing Identifier*, o *BCID*), entrambi gestiti da contatori sulle schede di *front end*. Dovranno essere trasmessi due segnali che permettano di mantenere la coerenza tra tali identificativi e gli eventi all'interno del rivelatore. Questi segnali sono l'*Event Counter Reset (ECR)* ed il *Bunch Counter Reset (BCR)*, il cui compito verrà illustrato in seguito.

Affinchè ci sia questo sincronismo tra i sistemi di elaborazione e il clock di macchina è cruciale, quindi, la realizzazione di un sistema di trasmissione in grado di garantire che il segnale di cadenza e gli altri segnali di controllo ( ad esempio le decisioni del trigger di livello 1 ) siano distribuiti a tutti gli elementi dell'apparato ATLAS, limitando al minimo skew e jitter dei segnali. Infatti, a causa delle dimensioni del rivelatore, il segnale di clock di riferimento deve essere trasmesso fino a centinaia di metri di distanza, a tutte le entità che costituiscono l'apparato. Questo è uno dei problemi affrontati per poter garantire che l'intera macchina funzioni a 40 MHz. Inoltre, la fase del clock distribuito a centinaia di destinazioni differenti può essere controllata solo entro un margine di pochi nanosecondi, inaccettabile per le esigenze di funzionamento dell'apparato ATLAS. Si rende quindi indispensabile l'uso di un sistema che permetta una risincronizzazione e che garantisca un ripristino del clock in seguito ad una perdita di sincronismo.

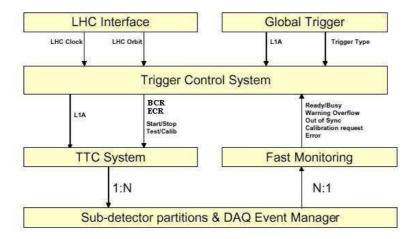

La figura 3.2 mostra l' insieme delle strutture di controllo progettate per l'acceleratore LHC ed in particolare il *Trigger Control System* ed il sistema *Timing Trigger and Control*.

Il *Trigger Control System* è l'entità che supervisiona la generazione dei segnali temporali e di trigger. Il *TCS* riceve dall'LHC il segnale di clock ed il segnale di orbita e riceve il segnale di validazione del livello 1 di trigger (LVL1Accept) dal Central Trigger Processor (CTP) dell'esperimento ATLAS.

Figura 3.2 L'architettura per la gestione dei segnali di controllo

Il *TCS* gestisce anche i segnali di *Reset (ECR* e *BCR)*, utilizzati per recuperare il sincronismo quando si verificano perdite di informazioni, dovute a una cattiva trasmissione o a problemi di immagazzinamento dei dati. Tali segnali sono trasmessi periodicamente o quando ne viene avanzata richiesta da uno dei sottosistemi che costituiscono l'apparato ATLAS, qualora si sia verificato un malfunzionamento. Un ulteriore compito del *TCS* è il controllo e la gestione di segnali di calibrazione, di sincronizzazione o di test per i sottosistemi dell'apparato. Per finire, il *TCS* si occupa anche della gestione di segnali di servizio, come *busy* ( che indica che il sistema è impegnato e non può ricevere un altro segnale di trigger), *out of sync* (che segnala che frammenti di eventi associati allo stesso *bunch crossing* non hanno gli stessi codici *EVID* o *BCID*) o segnali di errore.

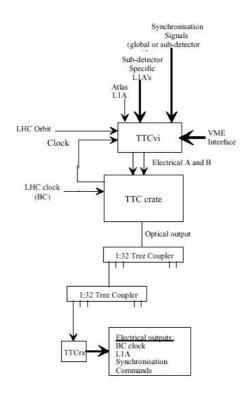

Il sistema *Trigger Timing and Control* (*TTC*) è responsabile della distribuzione dei segnali temporali e di trigger in tutto il rivelatore e alle differenti strutture di elaborazione dei dati. Il *TTC* riceve dal *TCS* il clock a 40 MHz, il segnale di orbita, i segnali *LVIA*, *BCID*, *EVID*, *BCR*, *ECR* e altri segnali di servizio. Tutti questi segnali sono codificati e trasmessi otticamente, tramite una struttura "ad albero", come è mostrato in figura 3.3, ai sistemi di elaborazione e verso le diverse destinazioni all'interno dell'apparato ATLAS. I segnali sono ricostruiti alla destinazione ed adattati

ai protocolli di funzionamento dei singoli rivelatori. Ad esempio, per il sistema di trigger di livello 1 nella regione di barrel, il sistema TTC è suddiviso in tre partizioni, una per  $\eta > 0$ , una per  $\eta < 0$  ed una per la sala di conteggio USA15, per un totale di 912 destinazioni complessive.

Figura 3.3 La struttura "ad albero" del TTC

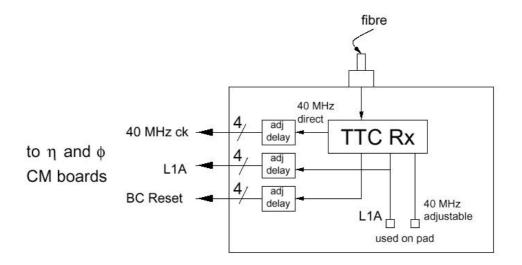

La distribuzione alle differenti unità costituenti l'apparato avviene attraverso la scheda TTCrx, mostrata in figura 3.4, che ricostruisce i segnali di Clock, LVL1A, Event Counter Reset e Bunch Counter Reset e li rende disponibili su quattro canali differenti per poter essere utilizzati dalle diverse strutture di elaborazione. La latenza di ricostruzione del TTCrx risulta essere di ~100 ns, mentre il jitter sul clock è di 100 ps.

A partire dai segnali del TTCrx, le schede dell'elettronica di acquisizione ( elettronica di *Front End* ) gestiscono due contatori che producono gli identificativi *Event Identifier* e *Bunch Counter Identifier*. L' *EVID* viene incrementato ogni volta che giunge il segnale *LVIID*, è codificato con 24 bit e contato a partire dall'ultimo *Event Counter Reset*. Il *BCID* viene

incrementato ad ogni *bunch* dell'orbita, è codificato con 12 bit ( $2^{12}$ = 4096, la potenza di 2 più prossima, in eccesso, a 3564) e viene contato a partire dall'ultimo *Bunch Counter Reset*. Questi due identificativi verranno indicati in seguito anche come *FEBCID* e *FEL1ID*, dove *FE* indica *Front End*.

Figura 3.4 Schema della scheda TTCRx

## La segmentazione dello spettrometro

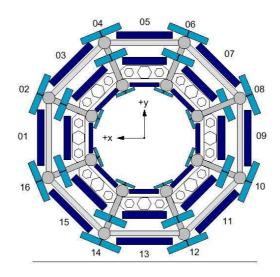

L'apparato ATLAS presenta una suddivisione dello spettrometro per muoni, nella regione di barrel e in direzione  $\varphi$ , in 16 differenti settori.

La figura 3.5 mostra tale suddivisione dello spettrometro eseguita a partire dalla struttura ottagonale del sistema magnetico. Ciascun settore corrisponde ad una regione azimuthale definita dalla disposizione delle bobine del magnete. Si individuano due tipi di settori, quelli occupati dalle bobine (indicati con numeri pari e detti "Small Sector") e quelli compresi tra due bobine adiacenti (indicati con numeri dispari e detti "Large Sector").

Figura 3.5 La segmentazione in settori dello spettrometro nella regione del barrel

A partire da questa suddivisione, il sistema di trigger e di acquisizione dati è segmentato in 64 settori logici. Infatti, dividendo in due ciascuno dei 16 settori *Large* o Small in cui è diviso lo spettrometro, vengono definiti 32 settori per  $\eta>0$  e 32 settori per  $\eta<0$ . Nelle zone di confine tra due settori adiacenti si presenta il problema della parziale sovrapposizione dei rivelatori: in tal caso, infatti, lo stesso muone può essere conteggiato due volte. Per risolvere il problema della sovrapposizione dei segnali in camere di rivelatori adiacenti, sono stati elaborati opportuni algoritmi di trigger e di acquisizione dati.

#### L'elettronica sui rivelatori RPC

L'elettronica di trigger e di acquisizione dati dei rivelatori RPC presenti nello spettrometro ( elettronica *on-detector*) è composta da schede ASD, dalle matrici di coincidenza CM e dalle schede PAD. Tali elementi verranno in seguito indicati come elettronica di *Front End*. I segnali prodotti dai rivelatori RPC sono raccolti dalle schede ASD (<u>Amplifier Shaper Discriminator</u>), che li amplificano, discriminandoli in ampiezza

secondo una soglia programmabile, e li formano in durata. Ciascuna scheda ASD riceve 8 canali di acquisizione.

Come discusso precedentemente, il sistema di acquisizione dei dati del rivelatore e di trigger deve essere sincronizzato col segnale di cadenza dell'acceleratore LHC. Questa richiesta è necessaria per le matrici di coincidenza CM e per le schede PAD, ma non per gli elementi di preamplificazione e discriminazione dei segnali dei rivelatori RPC. Infatti, il processo di formazione dell'evento, sebbene cadenzato dal *bunch crossing*, è intrinsecamente asincrono, poichè dipende dal tempo di volo del muone, dalla scarica nel rivelatore RPC e dal tempo di propagazione del segnale lungo le strip di lettura.

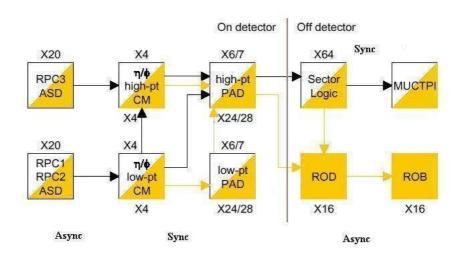

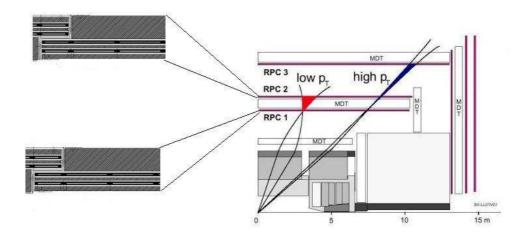

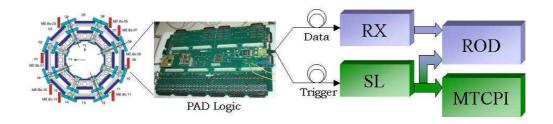

L'intero spettrometro comprende 64 settori logici, 1664 ROI, 416 schede PAD di " $low p_T$ " e altrettante di " $high p_T$ ". Le matrici di coincidenza CM utilizzano le informazioni in uscita dalle schede ASD per eseguire i due algoritmi di trigger, " $low p_T$ " ed " $high p_T$ ". I dati in uscita dalle CM sono ulteriormente elaborati dalle schede PAD che successivamente provvedono anche alla trasmissione verso i calcolatori che costituiscono i successivi livelli di trigger e di acquisizione: il percorso dei dati di rivelatore e di trigger è mostrato schematicamente in figura 3.6.

Figura 3.6 Lo schema dell'elettronica di acquisizione. Le linee chiare rappresentano i dati del rivelatore, le scure indicano i dati di trigger.

#### Le matrici di coincidenza

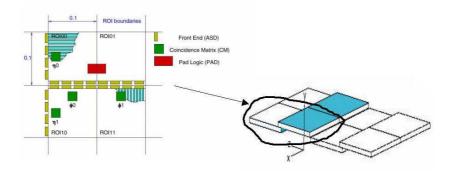

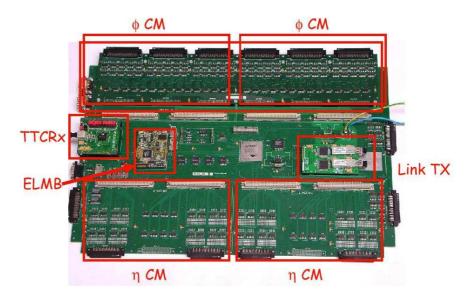

L'elettronica di trigger installata su ciascuna camera di rivelatori RPC è mostrata schematicamente in figura 3.7. Le schede ASD sono collocate alle estremità delle strip degli RPC, e sono connesse a pochi metri di distanza alle matrici di coincidenza CM a loro volta montate sulle schede PAD Logic. La figura 3.8 mostra la scheda PAD. Ogni scheda PAD ospita quattro matrici di coincidenza, relative ad una regione di granularità  $\Delta\eta \times \Delta\phi \approx 0.2 \times 0.2$ , oltre alla scheda TTCrx ed al modulo indicato con  $Link\ Tx$ , responsabile della trasmissione su fibra ottica dei dati del rivelatore e di trigger verso i successivi livelli di acquisizione.

Figura 3.7 L'elettronica sul rivelatore

Figura 3.8 La scheda PAD e gli elementi che la scheda può ospitare

Le matrici di coincidenza "low  $p_T$ " in direzione  $\eta$ , indicate in figura 3.7 come  $\eta$ 0 e  $\eta$ 1, ricevono da ognuno dei due piani di rivelatore mostrati nella figura 3.9, in ciascuna delle stazioni RPC1 e RPC2, segnali da 4 schede ASD che leggono ognuna otto strip  $\eta$ . In totale, dunque, ogni matrice CM, riceverà 8×4=32 canali da ciascun piano di RPC, ossia 32×4=144 canali di acquisizione, in direzione  $\eta$  e in eventi "low  $p_T$ ". Le matrici coprono un'area di granularità  $\Delta \eta \times \Delta \varphi \approx 0.1 \times 0.2$ . In queste regioni, un evento "low  $p_T$ " viene rivelato risolvendo le coincidenze definite tra i segnali dei quattro piani di rivelatore.

Figura 3.9 Disposizione dei rivelatori RPC del sistema di trigger

Come discusso nel capitolo precedente, la coincidenza è verificata in una matrice programmabile in funzione della soglia di momento trasverso impostata. Ogni scheda CM consente di programmare contemporaneamente fino a 3 diverse condizioni di trigger. Inoltre è possibile programmare la coincidenza a maggioranza 2/4, 3/4 o 4/4 tra i quattro piani di rivelatore. Ad esempio, nel caso di maggioranza 3/4, la condizione di trigger è valida soltanto se, all'interno della finestra di trigger, sono rilevati, in coincidenza in tempo entro 20 ns, almeno 3 dei 4 segnali ricevuti dalle due stazioni di trigger. Questo consente di ridurre in parte il rumore di fondo dell'apparato.

Una ulteriore reiezione del fondo si ha confermando l'evento, allo stesso modo accennato in precedenza, con i segnali delle strip  $\phi$ , orientate longitudinalmente.

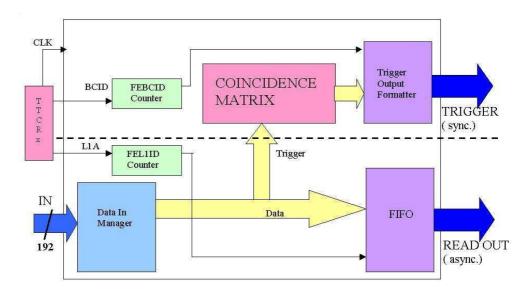

Figura 3.10 Schema a blocchi della matrice di coincidenza

La figura 3.10 mostra lo schema a blocchi della matrice di coincidenza CM. La matrice è stata progettata e realizzata in un ASIC (Application Specific Integrated Circuit ) dal gruppo di ricerca della sezione dell'Istituto Nazionale Fisica Nucleare e dell'Università "La Sapienza" di Roma. La scheda riceve in ingresso fino a 192 segnali (IN) provenienti dalle schede ASD ed i segnali BCID, L1A ed il clock a 40 MHz, ricostruiti dal TTCRx e gestiti da due contatori all'interno della CM. Le informazioni di trigger e dei dati seguono percorsi differenti, dopo essere stati trattati dalla logica di ingresso alla matrice di coincidenza. I dati del rivelatore ( Read Out ) sono immagazzinati in memorie FIFO (First In First Out) in attesa di essere trasmessi o meno ai successivi livelli di acquisizione ed elaborazione, in base alla decisione del trigger di livello 1; i dati di trigger vengono elaborati nella scheda in maniera sincrona e trasmessi ai processori di trigger. Quello che ci preme sottolineare è la differenza di fondo tra i due insiemi di dati: mentre i dati di trigger vengono trattati secondo un protocollo rigorosamente sincrono, scandito dal Bunch Crossing dell'acceleratore (40 MHz ), i dati del rivelatore seguono un protocollo asincrono, determinato dalla frequenza del segnale LIA ( ~ 100 KHz ).

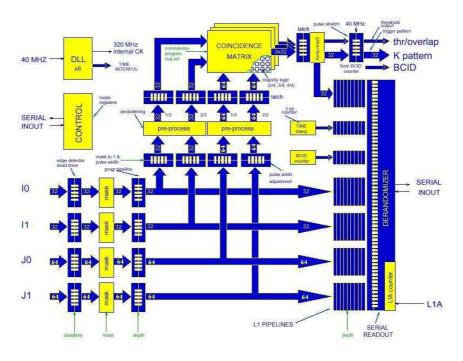

La figura 3.11 mostra uno schema a blocchi dettagliato dell'intero chip della matrice di coincidenza: gli ingressi sono indicati con I0 ed I1 ( i 32 bit di ciascun doppietto della stazione RPC1) e con J0 e J1 ( per il doppietto della stazione RPC2, o per il doppietto della stazione RPC3, nel caso "high  $p_T$ ", per il quale si prevede di poter usare fino a 64 bit). La frequenza di funzionamento interna di 320 MHz permette di suddividere ciascun periodo di clock in otto parti e consente una più accurata calibrazione del sistema. Si può notare, in ingresso, la presenza di tre blocchi differenti. Un circuito di dead-time introduce un tempo morto programmabile di poche decine di nanosecondi. Il compito del circuito di dead-time è evitare che più impulsi, entro la finestra temporale programmata, si presentino sullo stesso canale di ingresso. Esiste la possibilità di "mascherare", ossia di escludere i canali che non si intende esaminare perchè, ad esempio, rumorosi. Infine ci sono memorie "pipelines" la cui profondità è programmabile, necessarie per l'immagazzinamento e il corretto allineamento in tempo dei dati che, arrivando da postazioni differenti, giungono al chip in istanti diversi.

Figura 3.11 Lo schema a blocchi dettagliato della matrice di coincidenza

Dopo le memorie di ingresso, i dati vengono sdoppiati e trasferiti su due percorsi differenti, uno per il Read Out (la parte in basso, in figura) ed uno per il trigger, la cui uscita è costituita dalla parola di 4 bit thr/overlap, dal BCID a 12 bit e dal K-pattern a 32 bit, destinato agli ingressi J0 e J1 della matrice CM "high  $p_T$ " ma anche ad essere trasmesso, con i dati di read-out, verso i successivi livelli di acquisizione dei dati. I dati di read-out e il Kpattern sono immagazzinati in sette banchi di memoria, di profondità programmabile, in attesa della decisione del trigger di livello 1. Se c'è il segnale L1A, i dati sono promossi alle memorie FIFO (indicate in figura come "derandomizer") che li predispongono per l'uscita seriale, altrimenti sono eliminati. Le memorie devono mantenere i dati per la latenza del trigger di livello 1, cioè tutto il tempo in cui il trigger elabora i dati e decide se accettare o meno l'evento. Tale latenza dev'essere inferiore ai 2.5 us e poichè le memorie funzionano ad un clock di 320 MHz (~ 3.1 ns), la profondità delle memorie deve superare le 800 locazioni. I dati di trigger seguono un percorso più articolato. Vengono formati in durata (digital shaping & pulse width) per avere un livello superiore di sicurezza nell'eseguire la coincidenza tra i segnali. Infatti, poichè il funzionamento interno è di 320 MHz, per evitare false coincidenze tali segnali dovranno avere una durata che non supera i ~3.1 ns. Successivamente avviene il preprocessing, che esegue le operazioni a maggioranza 1/2 e 2/2, seguito da un registro che predispone i dati per la matrice di coincidenza vera e propria. La matrice esegue la coincidenza e le operazioni a maggioranza 2/4, 3/4 e 4/4. Come già precedentemente accennato, l'esistenza di una condizione di trigger è codificata in uscita nella parola di 4 bit (thr/overlap), che viene trasmessa alla scheda PAD, in cui sono riportate la più elevata soglia in momento trasverso validata dall'evento e l'eventuale presentarsi della coincidenza in regioni di sovrapposizione delle camere. Le matrici inoltre riproducono in uscita i 12 bit del contatore del BCID e, per l'algoritmo di "high p<sub>T</sub>", il K-pattern dalla stazione RPC1 che ha generato il segnale di trigger.

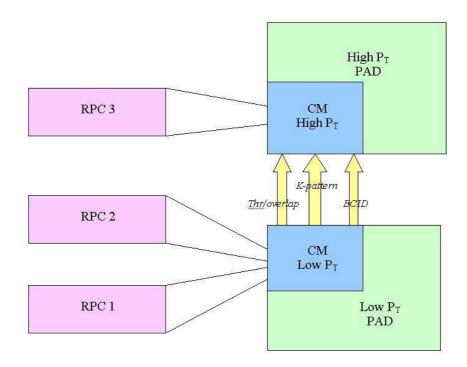

Così come per le matrici CM $\eta$ , le matrici di coincidenza  $\phi 0$  e  $\phi 1$  ricercano in queste regioni coincidenze tra i segnali dei 4 piani di rivelatore nelle stazioni " $low\ p_T$ " e coprono regioni di granuralità  $\Delta \eta \times \Delta \phi \approx 0.2 \times 0.1$ . In proiezione  $\phi$  non è imposta alcuna soglia sul momento dell'evento. L'unica condizione, dunque, è l'esistenza di una coincidenza dei segnali a maggioranza 2/4, 3/4, 4/4 entro un intervallo di tempo di 20 ns. Per analizzare gli eventi " $high\ p_T$ ", le informazioni sono trasferite alle corrispondenti matrici di coincidenza  $\eta 0$ ,  $\eta 1$ ,  $\phi 0$ ,  $\phi 1$  " $high\ p_T$ ", che sono installate sulle camere RPC3.

Figura 3.12 II flusso dei dati per l'algoritmo  $High p_T$

La matrice di coincidenza  $\eta 0$  "high  $p_T$ ", ad esempio, come mostrato in figura 3.12, riceve segnali dalla matrice di coincidenza  $\eta 0$  "low  $p_T$ ", e dai due piani di rivelatore nella stazione RPC3. L'algoritmo di coincidenza è lo stesso: anche in questo caso, dunque, come in un evento "low  $p_T$ ", la matrice ricerca una coincidenza in tempo entro intervalli di 20 ns tra i segnali in maggioranza 2/4, 3/4, 4/4 ed in finestre spaziali programmabili in funzione della soglia del momento trasverso imposto.

Inoltre, la matrice CM è programmabile per risolvere coincidenze a maggioranza 1/2, 2/2 tra i soli segnali della stazione RPC3 ed indipendentemente dall'occorrenza di un evento "low  $p_T$ ". Questo consente di confermare nei successivi livelli di logica del sistema di trigger un evento "low  $p_T$ ", per ridurre ulteriormente il rumore dell'apparato.

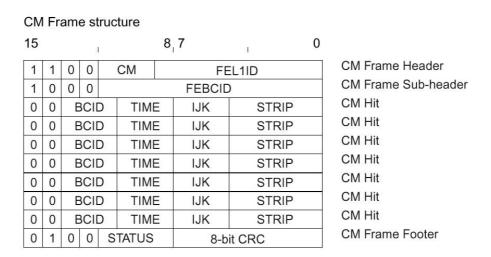

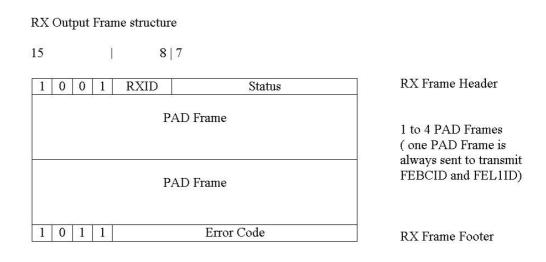

Il formato dei dati in uscita da ciascuna scheda CM è riportato in figura 3.13 e, come si vede, è organizzato in blocchi ("frame") composti da parole di 16 bit, i cui bit più significativi forniscono informazioni sul tipo di parola trasmessa. I quattro bit più significativi identificano gli "header" ed il "footer" del pacchetto, mentre le parole dati sono riconosciute se i primi due bit sono " 0 0 " . Queste parole contengono i dati sulle strip che hanno prodotto un segnale e informazioni relative ad uno degli intervalli (TIME) di 3.1 ns in cui viene diviso il periodo di clock, alla stazione di RPC relativa allla strip che ha prodotto il segnale ( IJK, dove I indica la prima stazione di RPC, J indica la RPC2 e K si riferisce alla RPC3 ), e tre bit (BCID) utilizzati per scopi di calibrazione e diagnostica. Negli "header" e "footer" sono contenute parole di controllo ( Status ed 8-bit CRC ), il codice identificativo della scheda ( CM ) e i due identificativi prodotti dai contatori di EVID e di BCID sulla scheda, il FELVID ed il FEBCID.

Figura 3.13 La struttura del frame prodotto dalla matrice di coincidenza

## Le schede PAD Logic

Le informazioni di due matrici " $low p_T$ " CM adiacenti in direzione  $\eta$ , e le corrispondenti informazioni delle due matrici CM in direzione  $\varphi$ , sono elaborate dalla scheda " $low p_T$ " PAD Logic. Per l'algoritmo di trigger " $high p_T$ ", invece, come mostrato in figura 3.12, i dati che arrivano alla scheda PAD Logic " $high p_T$ " provengono sia dalle CM "low" che dalle CM"high".

La scheda PAD Logic "low  $p_T$ " e le quattro CM "low  $p_T$ " sono montate sulla stazione RPC2, mentre la scheda PAD Logic "high  $p_T$ " e le quattro CM "high  $p_T$ " sono montate direttamente sulla stazione RPC3.

Una scheda PAD Logic copre una regione di granularità  $\Delta \eta \times \Delta \phi \approx 0.2 \times 0.2$ ; la dimensione di una *Region Of Interest* è, invece,  $\Delta \eta \times \Delta \phi \approx 0.1 \times 0.1$ : ogni PAD Logic conterrà, allora, informazioni su 4 ROI. Un settore *Small* dello spettrometro viene gestito da 7 PAD, mentre uno *Large* da 6 PAD.

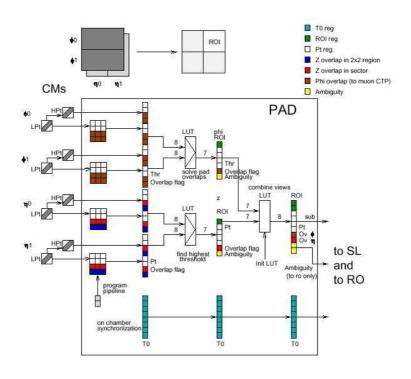

La figura 3.14 mostra lo schema a blocchi della scheda PAD Logic.

Figura 3.14 Schema a blocchi della scheda PAD Logic

Compito principale della scheda PAD è eseguire un'ulteriore elaborazione dei dati del rivelatore e del trigger prodotti dalle matrici di coincidenza CM. Tali dati sono combinati tra loro, producendo due pacchetti differenti di informazioni, per il trigger e per i dati, e sono inviati su fibra ottica alla sala di conteggio USA15. Mentre il protocollo di trasmissione dei dati di Read Out è asincrono ed è regolato dal presentarsi del segnale di L1A (~ 100 KHz), i dati di trigger sono trasferiti con protocollo sincrono, alla frequenza di bunch-crossing (40 MHz) e con una latenza piccola (per non saturare le succesive memorie *pipeline*) e fissata (per permettere una esatta calibrazione temporale del sistema di acquisizione). Gli altri compiti di una scheda PAD sono l'identificazione della Region Of Interest per un evento validato dal trigger, combinando le informazioni in  $\eta$  e in  $\varphi$ , e la trasmissione di informazioni di trigger (come le soglie in impulso impostate), del *BCID* e delle *flag* di sovrapposizione in  $\eta$  e in  $\varphi$ . Inoltre, tramite il *chip* TTCrx, ogni scheda PAD riceve i segnali *LVL1A*, *LVL1RST*, BCIDRST del TTC e li fornisce alle quattro matrici di coincidenza e alla logica della scheda PAD.

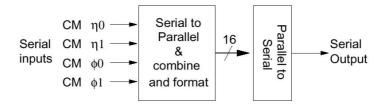

Per quello che riguarda l'elaborazione delle informazioni dalle matrici di coincidenza, la figura 3.15 mostra lo schema a blocchi del flusso dei dati all'interno della scheda PAD. La logica è gestita da una *FPGA* ( *Field Programmable Gate Array*) appositamente progettata. I dati prodotti dalle CM entrano nella *FPGA* in modo seriale, sono convertiti in parallelo e combinati in modo da formare parole da 16 bit. Per il trasferimento verso i successivi livelli di elaborazione, tali parole sono riconvertite in forma seriale dai dispositivi che gestiscono la trasmissione ottica.

Figura 3.15 Lo schema a blocchi per il flusso dei dati di read-out

La logica della scheda PAD Logic è strutturata secondo un modello "pipelined": le operazioni vengono eseguite in tre passi successivi. Nel primo passo i dati provenienti dalle matrici CM sono allineati in tempo; nel secondo vengono risolte le eventuali sovrapposizioni in  $\eta$  e  $\varphi$  e si calcola la soglia in momento trasverso più elevata; nel terzo passo i dati sono combinati e viene prodotta l'uscita. L'evento è confermato se è risolta una condizione di trigger sia in direzione  $\eta$  sia in direzione  $\varphi$ .

Se non è ricostruito un evento "high  $p_T$ ", inoltre, viene asserita la flag di stato OPL, che indica l'esistenza di una coincidenza a maggioranza 1/2 o 2/2 tra i soli segnali della stazione RPC3 all'interno delle ROI controllate dalla PAD.

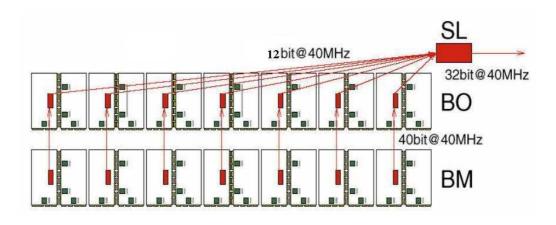

I dati prodotti da una scheda PAD sono inviati su due percorsi differenti, a seconda che siano dati di trigger o di *read out*. Le informazioni riguardanti il trigger saranno inviate, tramite link ottici, ad una scheda <u>Sector Logic</u> (SL), secondo un protocollo sincrono a 40 MHz. Le informazioni riguardanti un dato del rivelatore vengono trasmesse al <u>Read-Out Driver</u> (ROD), secondo un protocollo asincrono. C'è la necessità di un protocollo asincrono perchè, come già ampiamente discusso, i dati vengono trasferiti ai successivi livelli di acquisizione solo in presenza del segnale di *LV1A*, la cui frequenza attesa risulta essere di ~ 100 KHz. Le schede PAD, inoltre, trasferiscono alle schede SL parole in cui è codificata la condizione di trigger ricostruita nelle ROI controllate da ciascuna PAD.

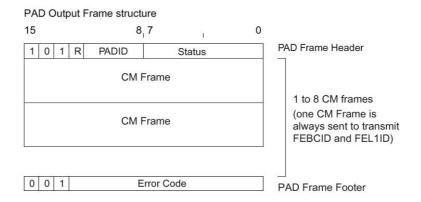

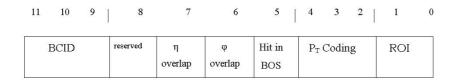

I dati prodotti dalle PAD hanno un formato differente, a seconda che siano informazioni di trigger (12 bit) o di dati, nel qual caso viene prodotto un nuovo pacchetto ("frame") di parole da 16 bit, che contiene da uno fino ad un massimo di otto *CM frames*. Un *CM frame* viene sempre trasmesso, anche in assenza di un evento interessante, per trasmettere *FEL1ID* e *FEBCID* (gli identificativi che sono generati dai contatori sulle schede di *Front-End*).

Figura 3.16 Il formato dei dati di Read Out in uscita dalla PAD

Figura 3.17 Il formato dei dati di trigger in uscita dalla PAD

Un *PAD frame* contiene un *header* ed un *footer*, che sono identificati dai valori dei tre bit più significativi, rispettivamente " 1 0 1 " e " 0 0 1". Il campo *header* contiene un identificativo della PAD ( *PADID*, di 4 bit ) ed un codice di controllo ( *status*, di 8 bit ). Il campo *footer* contiene un codice di errore ( 13 bit ). I formati delle uscite della scheda PAD, per i dati e per il trigger, sono mostrati nelle figure 3.16 e 3.17.

## Il percorso delle informazioni

I dati di una scheda PAD Logic vengono trasmessi tramite fibra ottica sia alle schede SL sia ai ROD. Il ROD ( <u>Read Out Driver</u> ) è l'entità responsabile della gestione ed elaborazione dei dati di *read out* provenienti dalle schede PAD di un settore ( <u>Large o Small</u> ) e del loro successivo trasferimento verso gli ulteriori sistemi di elaborazione dei dati. A scopo di diagnostica, il ROD acquisisce anche i dati delle schede SL.

Per i dati del trigger si rende necessario un sistema di trasmissione sincrono e con una latenza piccola e fissata. E' necessario che la latenza di trasmissione sia fissata e conosciuta, per poter calibrare tutti i successivi sistemi di acquisizione; inoltre, tale latenza dev'essere piccola, per limitare al minimo le dimensioni delle memorie "pipeline" che dovranno immagazzinare i dati nei successivi livelli di acquisizione e di elaborazione.

La figura 3.18 mostra il percorso che seguono le informazioni di trigger e quelle del *read out*. Mentre i dati sono raggruppati in parole di 16 bit ( più uno di *strobe*), le informazioni sul trigger sono trasferite in parole da 12 bit. Inoltre, mentre il percorso dei dati riguardanti il trigger dovrà essere rigorosamente sincrono, quello riguardante il *read out* dovrà essere asincrono, visto che i dati di interesse (e, di conseguenza, il *LVIA* ) non sono prodotti dal rivelatore ad ogni *bunch crossing*.

Figura 3.18 Il percorso dei dati dal rivelatore alla sala di conteggio

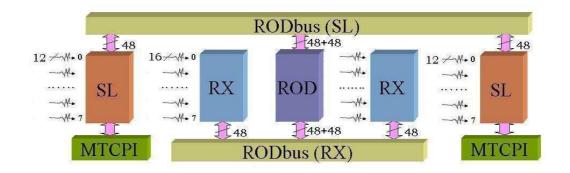

La figura 3.19 mostra la struttura del *crate VME*, situato nella sala di conteggio *USA15*, distante circa 80 metri dal punto di interazione dei fasci, che accoglie le schede *Sector Logic*, i concentratori ottici ( in figura RX) ed i ROD. Tenendo conto dell'ingombro dei connettori ottici e poichè in ogni *crate* ci sono 21 *slot*, ossia alloggiamenti per le schede, è ragionevole pensare di poter ricreare, in uno stesso *crate*, non più di due copie della struttura presentata in figura 3.19, controllate da una unità centrale, *CPU*, responsabile della gestione dell'intero sistema. Come si vede, ciascun ROD è in comunicazione, tramite *bus* dedicati (*RODbus SL* e *RODbus RX*), con due schede SL e due concentratori ottici. Le schede SL comunicano con il

ROD per questioni di diagnostica e trasmetteranno i loro dati verso il processore *MUTCPI* ( *Muon Trigger Central Processing Interface* ). Le schede RX ricevono i dati su fibra ottica dalle schede PAD, fino ad un massimo di otto, e dopo averli trattati li trasferiscono al ROD. Sia le schede SL che le RX trasmettono al ROD fino a 48 bit di dati: ad esempio, le schede RX trasmettono due blocchi da 24 bit, divisi in 16 bit di dati e 8 di controllo. Nei prossimi paragrafi si discuterà in dettaglio delle schede RX.

Figura 3.19 La struttura del crate

Ciascun ROD gestisce i dati provenienti da uno dei 32 settori in cui è diviso lo spettrometro ( considerandone la suddivisione in  $\eta>0$  e  $\eta<0$ ). Ognuno di questi settori corrisponde a 2 settori logici in cui è suddiviso il sistema di trigger, che sono gestiti ciascuno da 7 PAD ( se si tratta un settore *Small*) o da 6 PAD ( se è un settore *Large*). Il numero di PAD connesse ad un ROD, tramite le schede RX, sarà, quindi, dato da  $6 \times 2 = 12$  ( per un settore *Large*) oppure  $7 \times 2 = 14$  ( per un settore *Small*). Ogni scheda SL gestisce uno dei 64 settori logici dello spettrometro, ricevendo dunque le informazioni di trigger da 6 oppure da 7 PAD. In totale, dunque, saranno necessarie 32 strutture simili a quella mostrata in figura 3.19 per gestire il flusso di informazioni, di trigger e di *read out*, dell'intero spettrometro. Il ROD verrà descritto in maggior dettaglio nel corso di questo capitolo.

La figura 3.20, mostra l'event frame, ossia il "pacchetto" riguardante l'intero evento all'interno del rivelatore, che verrà costruito dall'Event Builder a partire dalle informazioni prodotte dal ROD ed elaborate dai livelli successivi di acquisizione dati. L'event frame è composto, a differenza degli altri frames, da parole da 32 bit.

| ent Frame      |               |

|----------------|---------------|

| 16             | 5 15 0        |

| Ma             | rker          |

| Sour           | ce ID         |

| Rese           | erved         |

| LVI            | .1 ID         |

| BC             | CID           |

| LVL1 Tri       | gger Type     |

| Detector I     | Event Type    |

| Status         | words         |

| RPC Data word  | RPC Data word |

| RPC Data word  | RPC Data word |

| RPC Data word  | RPC Data word |

| # Statu        | s Words       |

| 2000 30000000  |               |

| 1970/1970/1970 | Words<br>iler |

| 11.9           | iller         |

Figura 3.20 Il formato dell' event frame

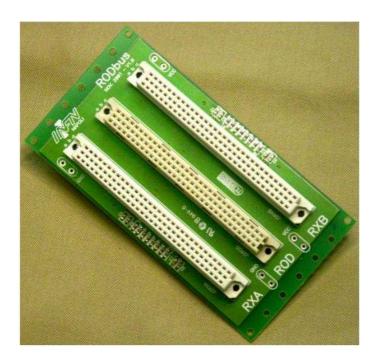

Per la progettazione del *backplane* destinato ad accogliere i due *bus* dedicati, si sono tenute in conto alcune richieste da rispettare. Per avere segnali che avessero un basso *skew* ed un basso *jitter* si rende necessario un approccio differenziale e, vista la necessità di dissipare poca potenza e avere notevoli prestazioni in frequenza, si è scelto lo standard LVDS. La figura 3.21 mostra un prototipo del RODbus, realizzato e collaudato presso i laboratori di ricerca dell' Università "*Federico II*" di Napoli e della Sezione di Napoli dell'*INFN*. Una estesa trattazione del sistema di

trasmissione dei dati sul *backplane* è riportata nel capitolo IV del presente lavoro di tesi.

Figura 3.21 Il prototipo del RODbus

## Il link ottico

Sulla base delle necessità per i due differenti percorsi delle informazioni su fibra ottica, per il trigger ed i dati, è stato sviluppato un sistema di trasmissione unico, il link ottico G<sup>2</sup>LINK, che soddisfi tutte le richieste.

La tabella 3.1 mostra il flusso medio dei dati tra i sistemi che costituiscono la parte della struttura di *DAQ* e trigger legata al presente lavoro di tesi e che sono stati descritti in questo capitolo.

| Connessione  | Banda passante del<br>link | Banda passante media |

|--------------|----------------------------|----------------------|

| da CM a PAD  | 10 Mbit/s                  | 3.0 Mbit/s           |

| da PAD a ROD | 640 Mbit/s                 | 200 Mbit/s           |

| da PAD a SL  | 640 Mbit/s                 | 480 Mbit/s           |

Tabella 3.1 Bande passanti delle connessioni tra i diversi sistemi costituenti la struttura di acquisizione

Nel caso specifico di ATLAS, si presenta la necessità di dover trasferire dati dalla scheda PAD sia verso il concentratore ottico, che poi li invierà al ROD, sia verso le schede Sector Logic. Mentre il concentratore riceverà le informazioni riguardanti i dati in parole da 16 bit, le schede SL riceveranno informazioni di trigger, sincrone, codificate in parole da 12 bit.

Il link ottico G<sup>2</sup>LINK si basa su un classico approccio seriale ed utilizza dispositivi commerciali. La frequenza di funzionamento risulta essere dell'ordine del GHz.

Il link utilizza il chip-set *HDMP-1032/1034* che gestisce la serializzazione e la deserializzazione dei dati. La parte opto-elettronica si basa sui dispositivi *HFBR-5912E* [5]. In figura 3.22 sono visibili schede TX ed RX, che ospitano i componenti elettronici e quelli ottici.

Figura 3.22 Le schede di trasmissione e ricezione dati

I trasduttori opto-elettronici funzionano alla frequenza di 1.25 Gbit/s, utilizzando laser VCSEL ( <u>Vertical Cavity Surface Emitting Laser</u>) con una

lunghezza d'onda di 850 nm. La tensione di funzionamento risulta essere di 3.3V e lo standard logico di ingresso e di uscita è il PECL (<u>Positive Emitter Coupled Logic</u>).

Il *chip-set* HDMP 1032/1034 è composto da un trasmettitore e da un ricevitore e la loro funzione è quella di serializzatore (TX) e deserializzatore (RX) per i 16 bit (+ 1 bit di *strobe*) che vengono forniti al *chip-set*. Il trasmettitore fornisce una uscita seriale differenziale in standard PECL; il ricevitore accetta la coppia di dati PECL e restituisce 16 bit dati più il bit di *strobe* in standard TTL.

La frequenza di clock dei dispositivi utilizzati può variare nell'intervallo 13÷70 MHz. Oltre ai 16 bit dati, che formano il campo dati (*W-Field* o *Word Field*), vengono trasferiti anche 4 bit di controllo, che costituiscono il cosiddetto *C-Field* (*Control Field*), per cui l'effettiva frequenza sulla fibra ottica risulta essere 20 volte superiore a quella di clock. Nel caso specifico di ATLAS, il link è usato alla frequenza di *bunch crossing* ( 40 MHz ), con una frequenza di trasmissione seriale di 800 Mbit/s.

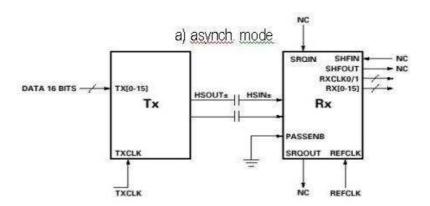

I serializzatori permettono la realizzazione di una architettura sincrona, in cui i clock del trasmettitore e del ricevitore hanno una precisa relazione di fase, oppure di una architettura asincrona, in cui non c'è nessuna relazione di fase tra i due clock.

Figura 3.23 La configurazione asincrona

Figura 3.24 La configurazione sincrona

Normalmente, i dati ricostruiti dal ricevitore vengono promossi in uscita sul fronte di salita del clock ricostruito, che è sincrono con il clock del trasmettitore. Se non c'è nessuna relazione di fase definita tra il clock del trasmettitore e quello del ricevitore, si presenta una situazione asincrona e l'unico modo per leggere correttamente i dati è usare memorie FIFO ( First In First Out). Se, invece, i due clock hanno solo una differenza di fase, legata ai diversi parametri fisici coinvolti ( ad esempio, la distanza tra i due dispositivi) è possibile leggere i dati utilizzando il clock del ricevitore oppure quello ricostruito. Le figure 3.23-24 riportano le due differenti configurazioni.

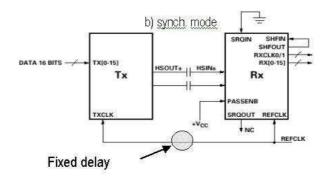

Figura 3.25 La latenza del G<sup>2</sup>LINK, in modalità sincrona

Nella modalità di funzionamento sincrona, la latenza del link, su 10 metri di fibra ottica, risulta essere di 165 ns, come riportato anche in figura 3.25.

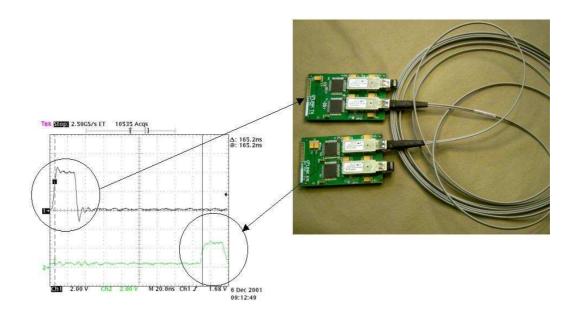

Tenendo conto delle già citate richieste per l'apparato ATLAS, la configurazione che soddisfa le esigenze del trasferimento dati sia per il trigger sia per il *read out* è quella riportata in figura 3.26.

Ciascuna scheda trasmettitrice ospita una coppia di trasmettitori ottici, è montata sulla PAD e gestisce la trasmissione verso concentratore ottico e Sector Logic.

Figura 3.26 La configurazione per la trasmissione sincrona di due parole a 16 bit

Il link ottico G<sup>2</sup>LINK è stato collaudato presso i laboratori di ricerca dell'Università "Federico II" di Napoli, e il sistema e le strategie di collaudo sono discussi nel capitolo V del presente lavoro di tesi.

## Le schede Sector Logic

Ciascuna scheda SL riceve, tramite i ricevitori G<sup>2</sup>LINK ospitati sulla scheda, ed elabora le informazioni di trigger di uno dei 64 settori logici in cui è diviso lo spettrometro nella regione di *barrel*. In un settore "*Small*

Barrel" i dati giungono a ciascuna SL da 7 PAD Logic, in un settore "Large Barrel" sono sufficienti 6 PAD Logic.

Ogni scheda Sector Logic si trova nella sala di controllo *USA15* e copre una regione di granularità  $\Delta\eta \times \Delta\phi \approx 0.2 \times 1.0$ , ricevendo le informazioni dalle schede Pad e dal trigger calorimetrico. L'uscita di ciascuna scheda SL viene inviata al *Muon Central Trigger Processor Interface (MCTPI)* ed al ROD per scopi di controllo e diagnostica.

Figura 3.27 Il percorso delle informazioni di trigger

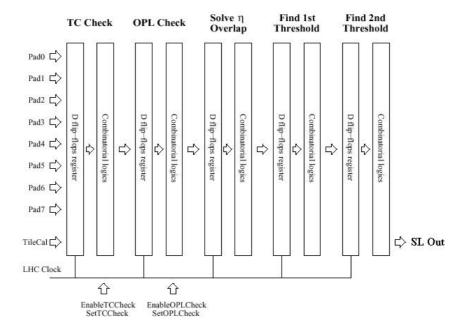

I compiti che una scheda SL svolge sono cinque:

- Confermare le informazioni di trigger delle PAD con i dati provenienti dal trigger calorimetrico. Un evento "low  $p_T$ " o "high  $p_T$ " è confermato richiedendo un segnale nei calorimetri adronici a scintillazione dell'apparato, all'interno del bunch-crossing di interesse. Studi in questo senso hanno infatti dimostrato una significativa efficienza del sistema nella separazione di muoni da elettroni e fotoni.

- Filtrare eventi del tipo "low  $p_T$ ", ossia identificare eventi "low  $p_T$ " a partire dai dati delle PAD di "low  $p_T$ " e dalle informazioni provenienti dalla terza stazione di trigger, che segnalano l'assenza di un evento "high  $p_T$ ". Così un evento "low  $p_T$ " è confermato se si riconosce asserita la flag di stato OPL in una almeno delle schede PAD corrispondenti.

- Risolvere le sovrapposizioni in direzione  $\eta$  e segnalare con una *flag* le sovrapposizioni in  $\varphi$  tra i diversi settori in cui è diviso lo spettrometro.

- Selezionare la traccia del muone con il più elevato  $p_T$ , riferendolo ad un univoco *bunch-crossing*. Inoltre, definendo una finestra in impulso intorno al più elevato  $p_T$  identificato, segnalare con una *flag* la presenza, in una regione identificata da una PAD, di più di un muone con l'impulso compreso in tale finestra

- Selezionare la traccia del muone con il secondo p<sub>T</sub> più elevato, riferendolo ad un univoco *bunch-crossing*. Inoltre, definendo una finestra in impulso intorno al valore del secondo p<sub>T</sub> più elevato, segnalare con una *flag* la presenza, in una regione identificata da una PAD, di più di un muone all'interno di tale finestra, oppure la presenza, in uno dei settori dello spettrometro, di più di due muoni all'interno di tale finestra.

Queste cinque funzioni logiche sono realizzate nella scheda in una architettura "pipelined", attraverso 5 step a 40 MHz, con uno step per ciascuna funzione logica. La figura 3.28 mostra lo schema a blocchi della architettura interna di una scheda SL.

Figura 3.28 Lo schema a blocchi della scheda Sector Logic

In figura 3.29 è riportato il formato dei dati in uscita da una scheda SL, strutturati in parole da 32 bit. Tali dai in uscita vengono inviati al MUCTPI su 32 coppie di linee di trasmissione, in standard LVDS. Per motivi di controllo e diagnostica, i dati prodotti dalla SL sono trasmessi anche al ROD attraverso un protocollo seriale, su un bus dedicato in standard LVDS.

| 0    | > 2 candidates in a sector |

|------|----------------------------|

| 15   | 1st candidate RoI          |

| 67   | 1st candidate reserved     |

| 89   | 1st candidate overlap      |

| 1014 | 2nd candidate RoI          |

| 1516 | 2nd candidate reserved     |

| 1718 | 2nd candidate overlap      |

| 1921 | 1st candidate pT           |

| 2224 | 2nd candidate pT           |

| 25   | > 1 candidate in RoI 1     |

| 26   | > 1 candidate in RoI 2     |

| 2729 | BCID                       |

| 30   | candidate 1 sign           |

| 31   | candidate 2 sign           |

Figura 3.29 Il formato dei dati in uscita dalla scheda Sector Logic

#### Il concentratore ottico

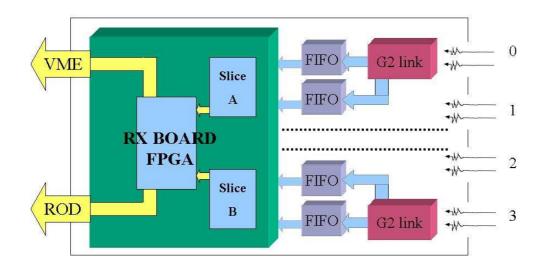

Le informazioni riguardanti i dati, prodotte dalle schede PAD, giungono alla sala di conteggio *USA15*, dove si trovano le schede RX destinate alla elaborazione dei dati e alla comunicazione con il ROD. Tali schede RX hanno come compito principale quello di ricevere i *frames* trasmessi dalle schede PAD attraverso connessioni ottiche multiple basate su G<sup>2</sup>LINK.

Inoltre una scheda RX può elaborare i dati che riceve dalle schede PAD, selezionandoli in funzione degli stessi parametri di *bunch-crossing*, introducendo dei bit di controllo aggiuntivi e producendo un unico "pacchetto" in uscita. Per questa ragione una scheda RX viene anche definita *concentratore ottico*.

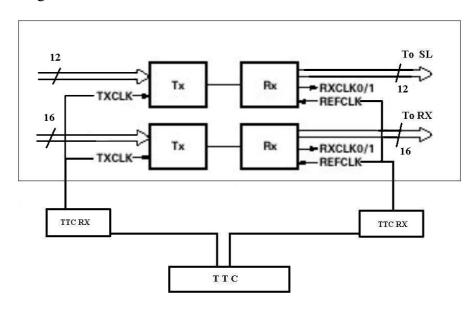

Figura 3. 30 La struttura del concentratore ottico

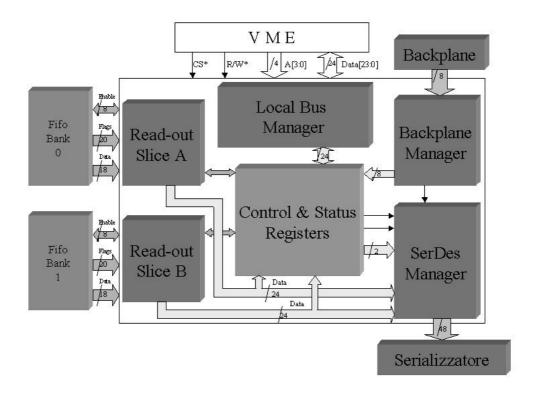

La figura 3.30 mostra lo schema del concentratore ottico, su cui sono alloggiati quattro moduli ricevitori di fibra ottica: poichè ciascun modulo ospita due trasduttori optoelettronici, su un concentratore ottico giungono fino ad 8 fibre ottiche, e quindi i dati provenienti da un massimo di 8 schede PAD. Come già evidenziato durante la trattazione sul link ottico, la trasmissione dei dati deve avvenire con un protocollo asincrono, e dunque si rende indispensabile l'uso di memorie *FIFO* (*First In First Qut*) per l'acquisizione dei dati provenienti da ciascuna PAD. La figura 3.31 mostra lo schema a blocchi del concentratore ottico, nel quale sono evidenziati i differenti elementi che gestiscono la logica.

La logica di ingresso è gestita dai due blocchi indicati con *Slice A* e *Slice B*, ciascuno dei quali acquisisce 18 bit ( 16 bit di dati + 2 bit di *strobe*) da una delle quattro *FIFO* che ogni *slice* può leggere. Con l'aggiunta di altri 6 bit di controllo all'interno di ciascuna *slice* si ottengono i 24 bit che ogni

*slice* invia, tramite serializzatori, sul backplane dedicato ( *RODbus RX*) verso il ROD.

Le principali informazioni legate al funzionamento del concentratore sono contenute nei registri *Control&Status Registers*, che oltre alle *flag* di stato delle *FIFO* ( *Empty FIFO* o *Full FIFO*) contengono anche informazioni sulle diverse procedure che il concentratore è in grado di eseguire, come la selezione tra comunicazione con *VME* o con il ROD, oppure le istruzioni per il funzionamento in modalità di diagnostica (*Self test*). Il concentratore esegue anche un controllo sulla corretta trasmissione dei dati, analizzando la sequenza di *header* e *footer* che sono contenuti nei *frames* di ingresso.

Figura 3.31 Lo schema a blocchi del concentratore ottico

L'entità all'interno di ciascuna *Read-Out Slice* consente di inviare i dati direttamente in uscita oppure effettua l'impacchettamento ( o "*framing*") dei diversi dati, selezionandoli e raggruppandoli in funzione degli stessi

parametri di *bunch-crossing*. Dati caratterizzati da uguali parametri temporali, anche se giunti in istanti differenti al concentratore, vengono così riuniti in uno stesso *frame*, che costituisce l'uscita del concentratore, il cui formato dei dati è riportato nella figura 3.32.

Figura 3.32 Il formato dei dati in uscita dal concentratore ottico

Le altre funzionalità del concentratore ottico consistono in una procedura di controllo del funzionamento del sistema di serializzazione dei dati, attraverso l'invio di *pattern* predefiniti sul *RODbus*, e in un sistema di comunicazione con un'interfaccia *VME*, che consente la lettura dei registri interni del concentratore ottico ma che è utile anche in fase di collaudo poichè consente di verificare l'integrità dei componenti e il corretto funzionamento della logica all'interno del concentratore.

Una trattazione dettagliata sul concentratore ottico è presentata nel capitolo IV del presente lavoro di tesi.

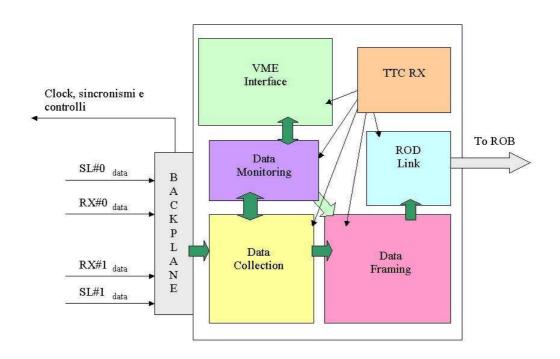

### II ROD

Il compito del ROD è di ricevere le informazioni ( *Data Collection* ) da ognuno dei due concentratori ottici con cui è in comunicazione ed eseguirne un ulteriore "impacchettamento" ( o *framing* ), prima di trasferirli ai successivi livelli di acquisizione, ossia ai *Read Out Buffer* ( ROB ). Il ROD comunica anche con le schede Sector Logic, per utilizzare anche le informazioni riguardanti il trigger nella procedura di *framing*. Come già accennato, il ROD gestisce anche i segnali di controllo del sistema di trigger e di acquisizione dati. A tale scopo, il ROD ospita un modulo TTCrx da cui riceve 8 segnali di controllo che trasmette alle schede RX e alle SL. Segnali di controllo sono, ad esempio, il *LVL1Accept*, o i segnali di reset *BCR* o *ECR*. Provvede, inoltre, alla distribuzione del clock sincrono al *bunch crossing* alle schede SL ed alle RX.

Oltre a ciò, il ROD è responsabile di eseguire controlli ( *Data Monitoring*) sull'integrità delle informazioni trasmesse, di rilevare errori nella trasmissione dati o disaccordo tra i codici *FEL1ID* e *FEBCID* ( i segnali generati dalle schede di *Front End* ) e i corrispondenti codici generati dallo stesso ROD, ossia *ROD\_L1ID* e *ROD\_BCID*, procedendo al ripristino del corretto sincronismo tra i dati. In particolare, per quello che riguarda le operazioni di controllo e di gestione degli errori, è presente sul ROD un'interfaccia VME, che permette ad un utente di:

- Eseguire una statistica su eventi ed errori ad ogni orbita di LHC.

- Controllare gli algoritmi di trigger utilizzando i dati raccolti per comparare gli eventi proposti dalla struttura *hardware* con modelli *software* di simulazione.

- Ispezionare le *flag* di occupazione ( *Almost Full* ) delle memorie FIFO della struttura di elaborazione, per introdurre tempo morto nel sistema di acquisizione dati.

• Controllare le *flag* di occupazione dei *Read Out Buffer* ( *ROB BUSY* ), per introdurre tempo morto nel ciclo di acquisizione dati.

Uno schema di principio del ROD è riportato in figura 3.33. Sono mostrati i blocchi principali, cui è necessario fare riferimento in fase di progettazione della scheda. Oltre alle caratteristiche già elencate, si può notare il blocco indicato con *ROD link*, che è responsabile della trasmissione dei dati prodotti dal ROD verso i ROB.

Figura 3.33 Lo schema a blocchi del ROD

## La simulazione del sistema di trigger

Il sistema di trigger dello spettrometro è stato simulato per verificare che potesse soddisfare le richieste imposte.

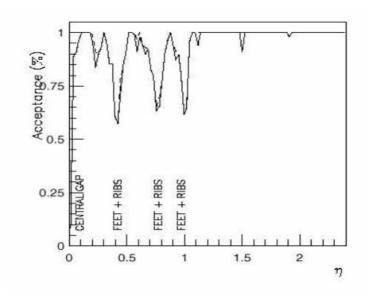

In figura 3.34 è riportata, in funzione di  $\eta$ , nella regione di pseudorapidità  $|\eta| < 2.4$ , l'accettanza del sistema integrata in  $\varphi$ . Le regioni in cui

l'accettanza è inferiore al 75% sono caratterizzate prevalentemente dalla presenza delle strutture di supporto e delle zone di accesso all'apparato.

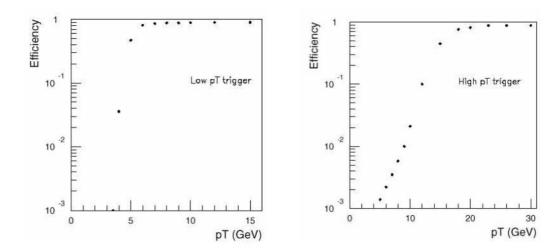

Inoltre, imponendo che siano rivelati il 90% dei muoni generati con energia di soglia entro l'accettanza del rivelatore, sono state definite le dimensioni delle finestre di coincidenza negli eventi "high  $p_T$ " e "low  $p_T$ ". E' stata quindi stimata l'efficienza del sistema come il rapporto tra il numero di muoni rivelati ed il numero di muoni generati. I valori di efficienza attesi sono riportati in figura 3.35, ottenuti con soglie di "low  $p_T$ " = 6 Gev/c e "high  $p_T$ " = 20 Gev/c.

Figura 3.34 L'accettanza del sistema di trigger dello spettrometro

Sono state stimate inoltre le frequenze di trigger attese dai diversi eventi valutando l'efficienza del sistema e le sezioni d'urto di produzione di  $\mu$  previste in interazione protone-protone.

La frequenza complessiva attesa, in particolare, è inferiore al limite di ~100kHz imposto dalle specifiche del trigger di livello 2 dell'esperimento.

Figura 3.35 Efficienza del trigger per muoni a basso  $p_T$  (a sinistra) e ad elevato  $p_T$  (a destra)