# Tecniche automatiche di acquisizione dati

Digitalizzazione delle informazioni

# Acquisizione di segnali per l'elaborazione digitale

- Il segnale generato dai trasduttori in genere non è idoneo per la diretta elaborazione da parte dell'unità di governo che realizza un algoritmo di controllo

- Come visto nella lezione precedente c'è spesso bisogno di un'elettronica di condizionamento del segnale.

- Il segnale va poi filtrato in modo da permettere il campionamento corretto della grandezza da misurare (filtri anti aliasing)

- Spesso, per ragioni di economia, più segnali sono acquisiti dal medesimo canale ed è necessaria l'operazione di "multiplexing"

- Infine bisogna campionare i segnali e convertirli

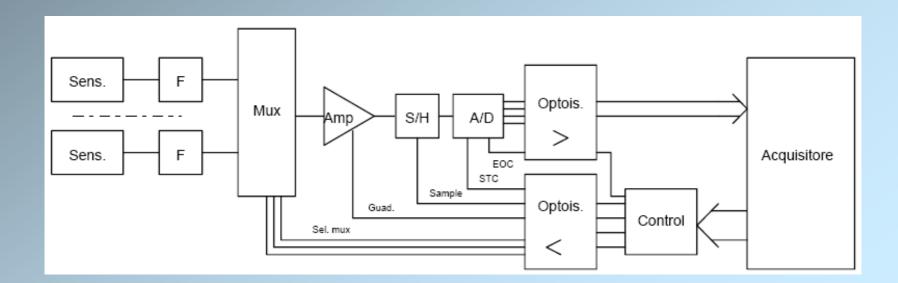

#### La catena di misura

- Per quanto detto, la catena di misura risulta dall'interconnessione dei seguenti dispositivi:

- Sensore

- Filtro

- Multiplexer

- Amplificatore

- Sample and Hold

- Convertitore analogico/digitale

- Logica di controllo (hardware e/o software)

- Acquisitore (computer)

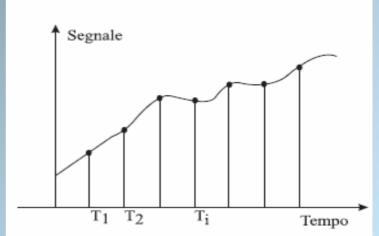

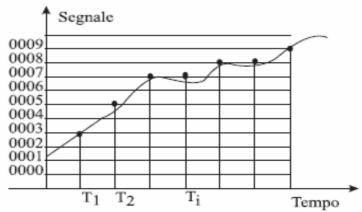

# Errore di acquisizione ed elaborazione digitale del segnale

- il campionamento non introduce un degrado dell'informazione del segnale,

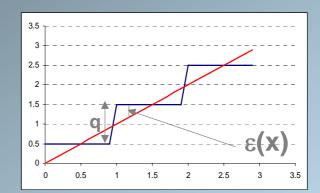

- la quantizzazione comporta un errore sul segnale acquisito

- Se ΔY è l'intervallo di uscita del trasduttore e lo rappresentiamo con un numero di N bit => l'errore massimo di quantizzazione è:

$e_q$  =LSB/2 Essendo LSB il bit meno significativo:

$$LSB = \Delta Y/2^{N}$$

Figura 2.3: Segnale campionato

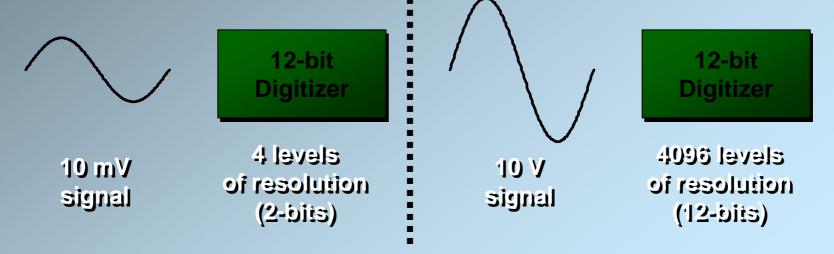

### Necessità dell'amplificazione

• Aumenta la risoluzione della misura

# Necessità dell'amplificazione II

Aumenta il rapporto segnale-rumore (Signal-to-Noise Ratio - SNR)

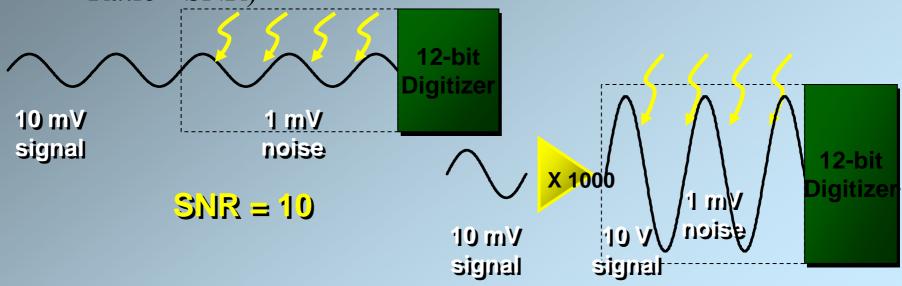

# Andamento spettrale di segnali campionati

- Un segnale ha una rappresentazione *spettrale* |X(f)|;  $X(f) = \underbrace{trasformata\ di}_{Fourier\ di} x(t)$

- Un segnale x(t) digitalizzato alla frequenza  $f_s$  ha una rappresentazione spettrale uguale a quella di x(t) spostata ad ogni  $f_s$

- Se X(f) non è =0 per  $f > f_s/2$ , c'è sovrapposizione degli spettri

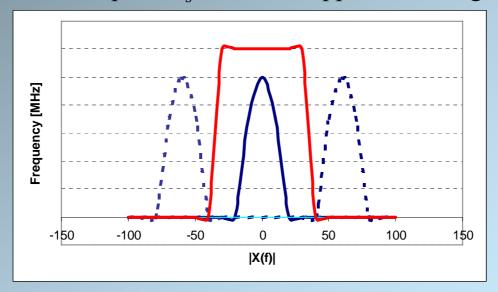

### Esempio

- Segnale: un impulso che sale in 10 ns e scende in 10 ns

- Effetto del campionamento a 10 e 20 MHz

100

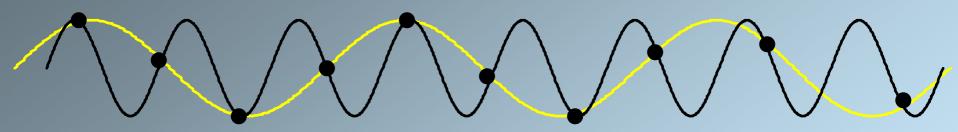

# Aliasing

- Il sottocampionamento può far sì che segnali di alta frequenza appaiano come segnali di frequenza inferiore (aliasing).

- Una volta che il segnale ha subito aliasing non è più possibile recuperare il segnale originale.

#### Teorema di Nyquist o di Shannon

- Per evitare la sovrapposizione di componenti spettrali (aliasing di campionamento), la frequenza di campionamento deve essere  $f_s \ge 2f_{max}$ , essendo  $f_{max}$  la larghezza dello spettro del segnale originario.

- La frequenza 2f<sub>max</sub> è detta frequenza di Nyquist

# Filtri anti aliasing

- Se ci sono componenti di rumore con frequenza maggiore di f<sub>max</sub> e il campionamento viene effettuato con frequenza prossima a quella di Nyquist, il rumore si sovrappone al segnale di interesse (Aliasing da disturbo): due soluzioni

- 1. Filtro passa basso prima del campionamento (antialiasing)

- 2. Aumento della frequenza di campionamento (sovracampionamento) e filtraggio digitale successivo.

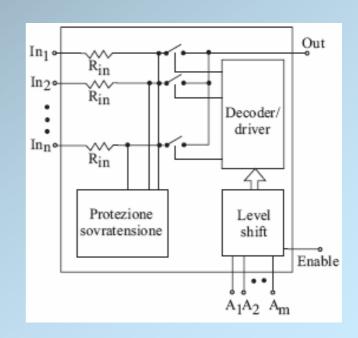

## Multiplexer

- È un dispositivo che commuta n canali in ingresso in uno in uscita

- La commutazione viene comandata da un segnale digitale che codifica il canale di ingresso da selezionare.

- Può essere a canale singolo o a canale differenziale

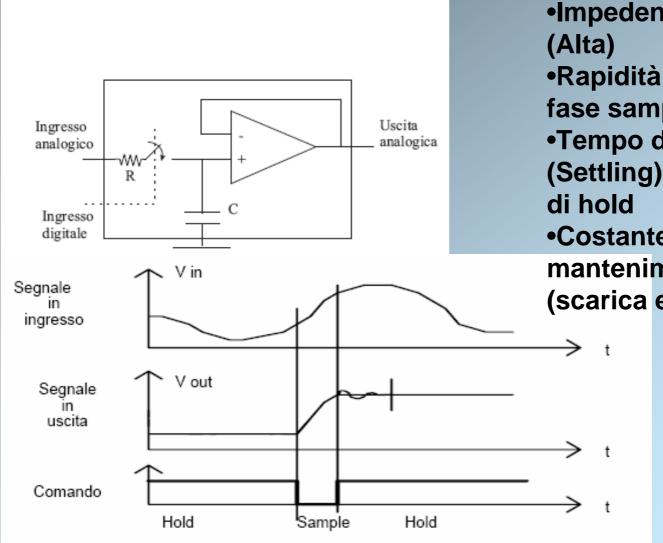

## Sample and hold

- I circuiti di campionamento e tenuta (sample and hold S/H) servono a mantenere fisso il valore del segnale campionato nel tempo in cui il convetritore A/D esegue la conversione

- È necessario quando la variazione del segnale durante il tempo di conversione è > LSB

- Dal punto di vista logico, il S/H è caratterizzato da due fasi:

- 1. La fase di sample (o anche track) riporta in uscita il segnale con guadagno unitario

- 2. La fase di tenute (hold) il valore del segnale ad un certo istante viene mantenuta costante.

### Samle and Hold II

- •Impedenza di ingresso (Alta)

- •Rapidità di adattamento in fase sample (Slew-Rate)

- Tempo di assestamento (Settling) dopo il comando di hold

- •Costante di tempo del mantenimento in hold (scarica esponenziale)

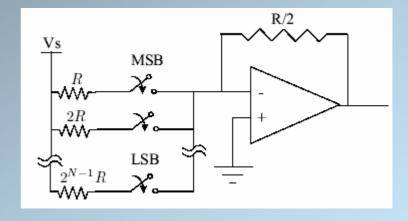

# Convertitori digitale Analogico (DAC)

- Converte una parola binaria in una grandezza elettrica analogica (tensione o corrente)

- Il fondo scala è il massimo valore binario rappresentabile  $2^{N}$ -1 (N = numero di bit)

- Se  $V_s$  è la massima tensione di uscita e x il numero da convertire =>  $V_o$ = x  $V_s/2^N$

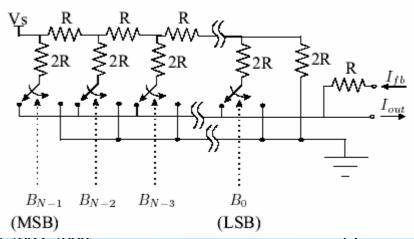

### Convertitori DAC II

- Dal punto di vista costruttivo è una rete resistiva: R, 2R, 4R...2<sup>N-1</sup>R unita ad un sommatore

- Difficilmente si trovano resistenze di valore esattamente pari ai multipli richiesti => si usa una rete composta da sole resistenze R e 2R

- La corrente nella prima resistenza a sinistra vale  $I_1=V_s/2R$ , quella nella seconda resistenza verticale vale  $I_2=I_1/2...I_N=I_1/2^{N-1}$ .

- I<sub>N</sub> è il bit meno significativo e I<sub>1</sub> il MSB.

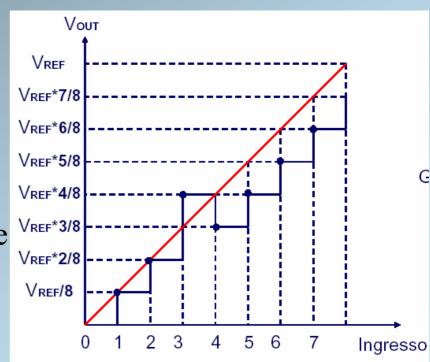

### Caratteristiche del DAC (e non solo)

- **Risoluzione**: Numero di bit in ingresso

- Accuratezza relativa o

Linearità: deviazione dalla

caratteristica ideale

- Non linearità differenziale:

La caratteristica ideale prevede

che l'uscita corrispondente a

ciascun numero in ingresso

differisca da quello adiacente

di un LSB

### Caratteristiche del DAC II

- Errore di guadagno: Differenza tra il valore di uscita reale e quello ideale

- Corrente di leakage i uscita: corrente misurata in uscita per ingresso nullo.

- **Settling time**: tempo impiegato alla corrente di uscita per stabilizzarsi al valore di regime entro ±0.5 LSB dopo una variazione

- **DA glitch impulse**: Impulso generato dalla variazione di molti bit non tutti nello stesso momento (si misura in V/s)

# Convertitori Analogico Digitale (ADC)

- Convertono una grandezza elettrica in un numero binario proporzionale.

- Ad integrazione

- A rampa

- A doppia rampa

- In retroazione

- Contatore

- Approssimazioni successive

- Sigma Delta  $(\Sigma \Delta)$

- Conversione diretta o parallela

- Flash ADC

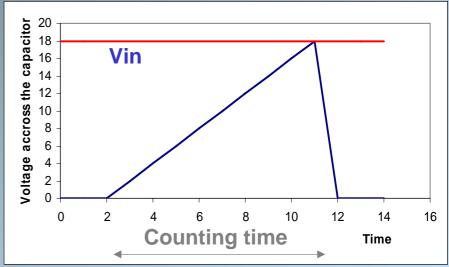

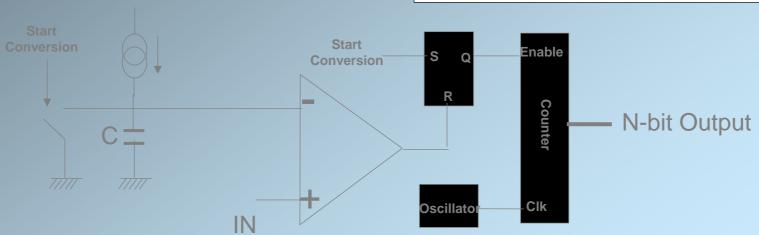

# ADC ad integrazione a rampa singola

- Comincia a caricare un condensatore con un a corrente costante.

- Conta i colpi di clock nel tempo di carica

- Ferma il conteggio quando la tensione sulla capacità raggiunge l'input

- Non può arrivare a grandi risoluzioni

- Capacità

- Comparatore

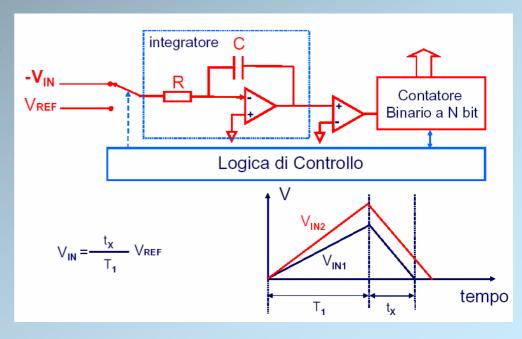

### ADC ad integrazione a doppia rampa

- Misura rapporti tra tempi di carica e scarica di un condensatore

- La capacità è caricata con una corrente proporzionale a V<sub>in</sub> in un tempo fissato

- Conta i clock nel tempo di scarica

- Precisione data dal rapporto di parametri

- Integranti

- Lenti (50 200 ms)

- Alta risoluzione (14 16 bit)

- Economici

### ADC ad approssimazioni successive

#### **METODO**

- Si sceglie un valore digitale a metà del campo di valori

- Si converte in un segnale analogico

- Si confronta il segnale analogico con l'ingresso

- In base al confronto si cambia il valore di prova

#### CARATERISTICHE

- Costo relativamente basso

- Buona velocità 1 50 μs

- Risoluzione 8 16 bit

- Non integra (richiede S/H)

- Rischi di non liearità differenziale e non monotonicità

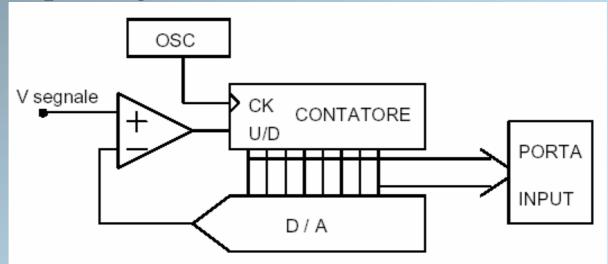

# ADC a Contatore (Tracking)

- Il valore di prova viene aggiornato continuamente con incrementi o decrementi

- Il valore del contatore può essere letto in ogni momento

- Adatto per segnali lenti

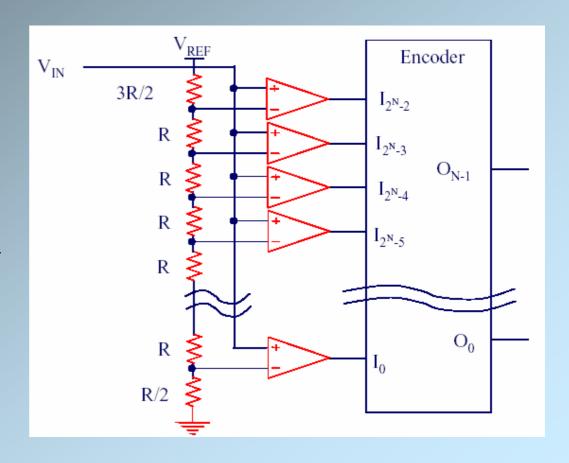

### Flash ADC

- Si fa il confronto con 2<sup>N</sup> comparatori ed altrettanti riferimenti

- Molto veloci: 100 500 ns

- Bassa risoluzione 4 –

10 bit

- Costo elevato: 1 comparatore per ciascun bit!!!

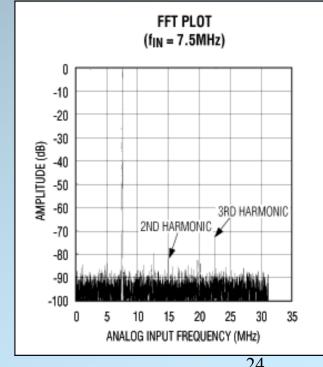

### Numero di bit effettivi

Un ADC an n bit introduce un errore di quantizzazione:

$$\varepsilon = \frac{q}{\sqrt{12}}$$

La conversione di un segnale (A/2) sinωt essendo A il fondoscala darà un errore:

$$\overline{\epsilon^2} = \frac{q^2}{12} = \frac{A^2}{122^{2n}}$$

Signal to Noise Ratio

$$SNR=10\log\left(\frac{\overline{x^2}}{\overline{\epsilon^2}}\right)=10\log\left(\frac{\frac{A^2}{8}}{\frac{A^2}{122^{2n}}}\right)=6n+1.8dB$$

- Numero effettivo di bit di un FADC a n-bit

- n' che da il corretto SNR

- Esempio: 12-bit da 20 a 65 MHz

- Fissiamo SNR = 70 dB

- Effective number of bits = (70-1.8)/6 = 11.4

$$\varepsilon^2 = \frac{1}{q} \int_{-\frac{q}{2}}^{+\frac{q}{2}} x^2 \, dx$$

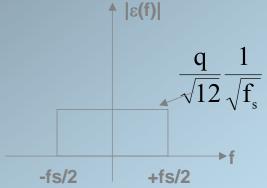

## Over-sampling ADC

$$-\frac{q}{2} \le \varepsilon \le +\frac{q}{2}$$

$$\varepsilon^{2} = \frac{1}{q} \int_{-\frac{q}{2}}^{+\frac{q}{2}} x^{2} dx = \frac{q^{2}}{12}$$

- Assumendo che l'errore  $\varepsilon$  sia rumore bianco, la sua PSD è piatta nell'intervallo  $[-f_s/2,f_s/2]$

- Se f<sub>s</sub> è maggiore della frequenza f<sub>0</sub> del segnale da misurare, allora, dopo il filtraggio l'errore sarà diventato:

$$\varepsilon \sqrt{\frac{f_0}{f_s}} = \frac{A}{2^n} \frac{1}{\sqrt{12}} \sqrt{\frac{f_0}{f_s}}$$

with A being the full scale and n the number of bits

# Over-sampling ADC (cont)

• Il Rapporto Segnale-Rumore quando si converte un segnale (A/2) sinωt, essendo A la scala, sarà

$$SNR=10\log\left(\frac{\overline{x^2}}{\overline{\varepsilon^2}}\right)=10\log\left(\frac{\frac{A^2}{8}}{\frac{A^2}{12 \ 2^{2n}} \frac{f_0}{f_s}}\right)=1.8+6n+10\log\left(\frac{f_s}{f_0}\right) dB$$

SNR = 1.8 + 6n'

n' being the effective number of bits

- Quindi è possibile aumentare la risolutione aumentando la frequenza di campionamento e filtrando.

- Esempio:

Un ADC a 8-bit diventa a 9-bit ADC con un fattore di sovracampionamento di 4

Ma l'ADC a 8-bit deve soddisfare I requisiti di linearità di un ADC a 9-bit

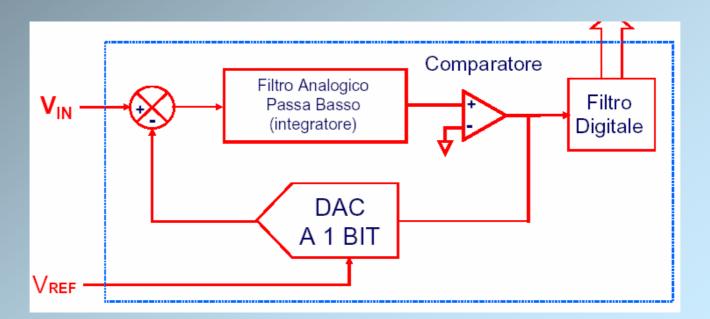

#### ADC $\Sigma - \Delta$

- Sovracampionamento e filtraggio digitale passa basso

- Si può generalizzare con un ADC ad approssimazioni successive con DAC ad 1 bit

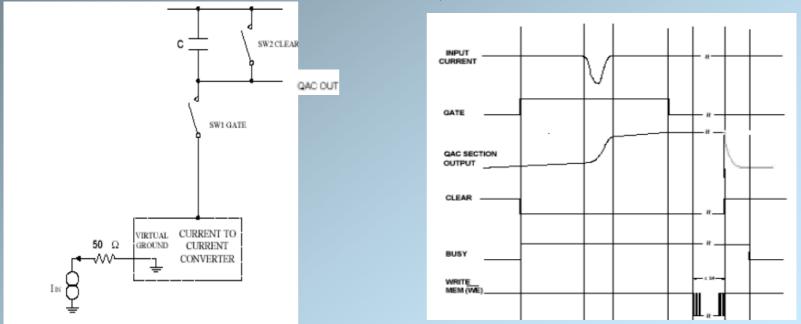

### Charge to Digital Converter - QDC

- Misura la carica (l'integrale della corrente nel tempo) di un segnale che cada al'interno di un segnale detto di gate.

- È composto da un convertitore carica-ampiezza (QAC essenzialmente un circuito RC) e da un ADC.

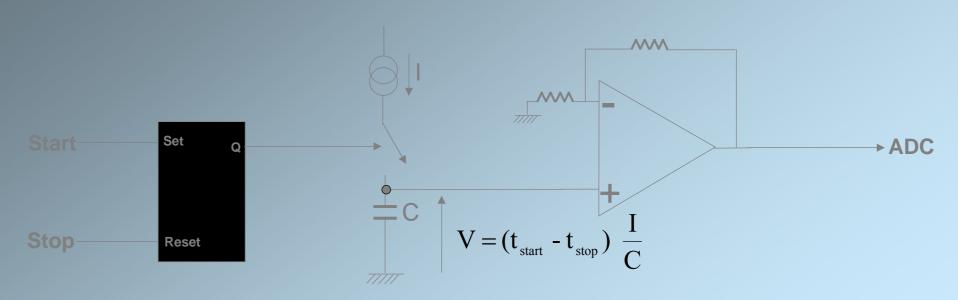

# Time to Digital Converter

- È essenzialmente costituito da un clock ed un contatore.

- Il contatore è abilitato a partire da un impulso di start e fino ad un impulso di stop.

- La risoluzione temporale è data dal fondoscala cioè dalla massima differenza tra start e stop, che spesso è regolabile: r=f/2<sup>N</sup>.

# Esempio TDC

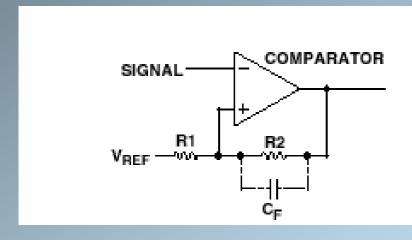

### Discriminatori

- Da un segnale impulsivo dobbiamo ricavare un istante di start o di stop.

- Input = Segnale analogico

- Output = segnale digitale

- Dopo un titardo fisso, se possibile

- Se il segnale passa una soglia

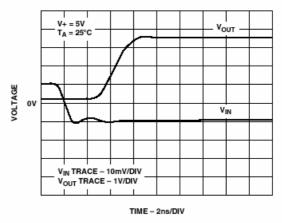

- discriminatore ≈ amplificatore ad alto guadagno

Figure 15. Rising Edge Response

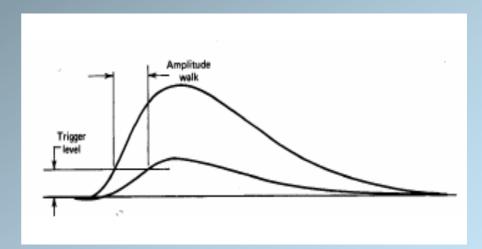

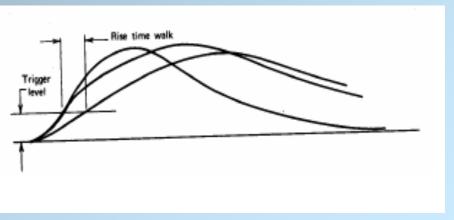

### Time Walk

- Differenza di tempo dovuta al passaggio della soglia. Può dipendere

- Dall'ampiezza

- Dal tempo di salita.

#### Constant Fraction Discriminator (CFD)

- Serve a risolvere il problema del time walk

- Produce un segnale logico dopo che il fronte di salita ha raggiunto una percentuale costante del picco.

- 1. Si prende il segnale e lo si moltiplica per una frazione f

- 2. Si inverte il segnale di ingresso e lo si ritarda di più del tempo di salita

- 3. Si sommano i due segnali di 1. e 2.

- 4. Il segnale in uscita parte quando la somma passa lo zero, che corrisponde a quando il segnale raggiunge una frazione f del picco e, a parità di forma è indipendente dall'ampiezza.